miniHDL: A Python Hardware Description Language DSL

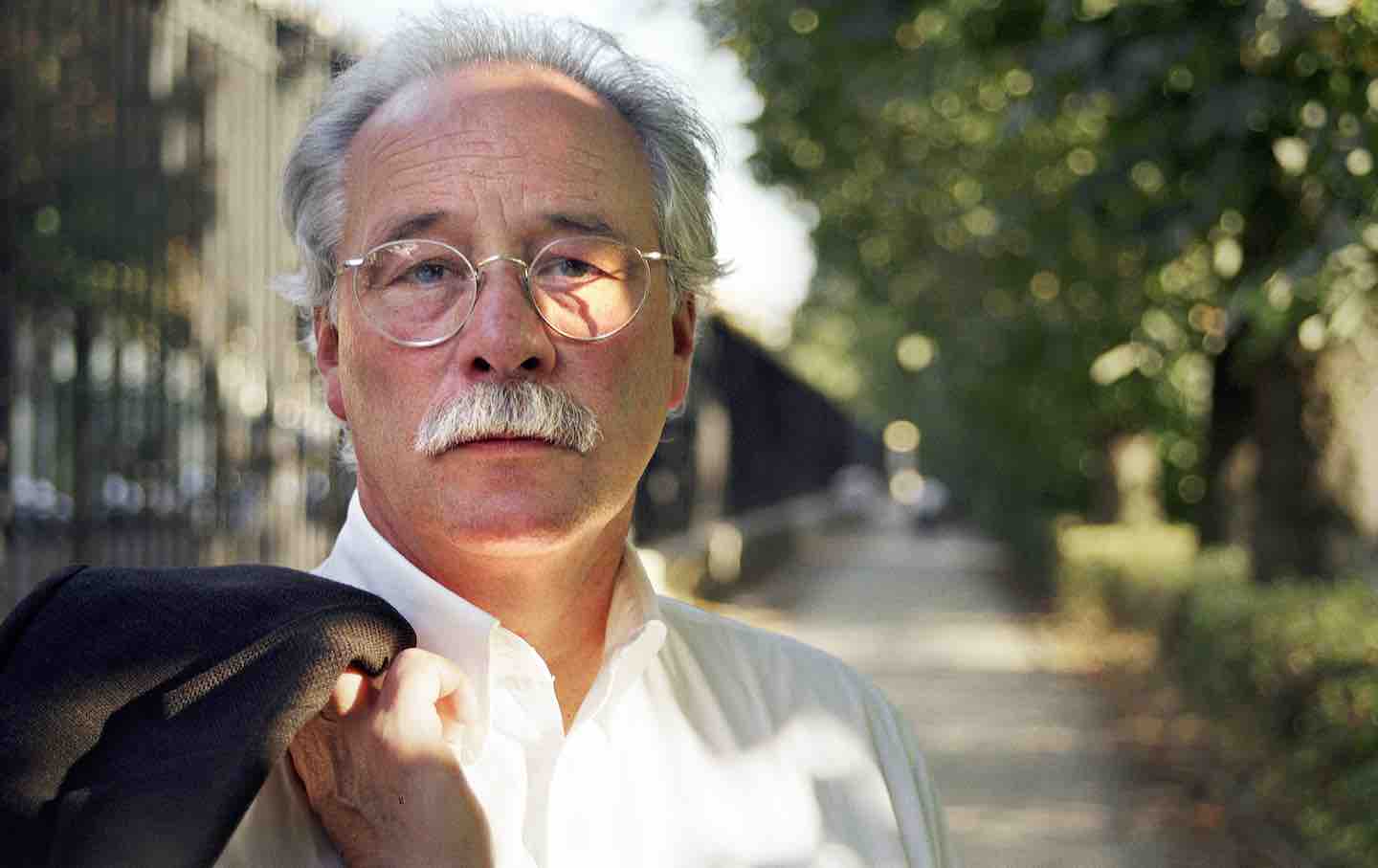

by Nicholas Carlini 2025-07-31

Hardware description languages (like Verilog or VHDL) have always confused me. This is despite the fact that they're just another programming language, albeit one that describes how to connect logic gates together instead of how to perform some dynamic computation. Probably this is just a skill issue on my part. I decided a while ago that I wanted to learn this dark art, and since the best way to learn anything is to build it from scratch, in this article I want to walk through the design of miniHDL, a python domain-specific language I wrote. In order to be as simple as possible, this HDL is meant to generate circuits that work in a determinsitic simulator; lets me write much simpler idealized circuits than you can write in practice. [a] For example, my clock will be some not gates connected toether, the HDL it doesn't care about clock domain crossing, can't represent unknown X or Z states, etc etc. In fact, if you know what those words mean, you probably are going to have a bad time reading this post.

This is the first in a two-part series of articles. I mainly wrote this article because the next part I'm preparing to upload just crossed ten thousand words... and so I decided to pull this HDL piece out of it to make the second part more readable. So look forward to that coming soon. For now it's top secret though.