The NEORV32 RISC-V Processor: Datasheet

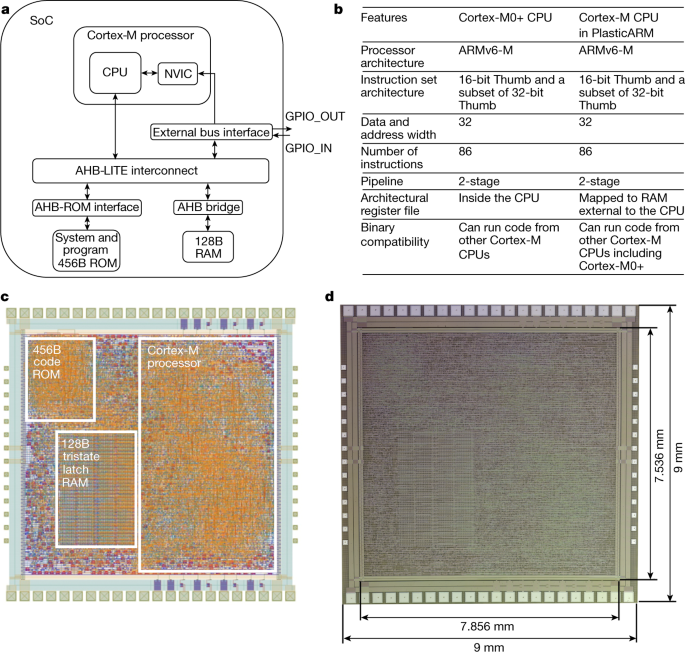

The NEORV32[1] is an open-source RISC-V compatible processor system that is intended as ready-to-go auxiliary processor within a larger SoC designs or as stand-alone custom / customizable microcontroller.

The system is highly configurable and provides optional common peripherals like embedded memories, timers, serial interfaces, general purpose IO ports and an external bus interface to connect custom IP like memories, NoCs and other peripherals. On-line and in-system debugging is supported by an OpenOCD/gdb compatible on-chip debugger accessible via JTAG.

The software framework of the processor comes with application makefiles, software libraries for all CPU and processor features, a bootloader, a runtime environment and several example programs - including a port of the CoreMark MCU benchmark and the official RISC-V architecture test suite. RISC-V GCC is used as default toolchain (prebuilt toolchains are also provided).

I am fascinated by processor and CPU architecture design: it is the magic frontier where software meets hardware. This project has started as something like a journey into this magic realm to understand how things actually work down on this very low level.

/cdn.vox-cdn.com/uploads/chorus_asset/file/25255988/246965_vision_pro_AKrales_0140.jpg)