TSMC bets big on 2nm by 2025 – but can it deliver?

analysis Over the last couple of weeks, TSMC's ambitious roadmap for its 2nm manufacturing process has sparked significant attention. The chipmaker is set to begin the mass production of its 2nm process node in 2025.

Amid the furor and speculation, it remains unclear when 2nm can realistically start rolling off production lines. With much talk of geopolitics, location, and timescales, just how grounded is TSMC's claim that it's going to turn on the assembly line of 2nm wafers next year?

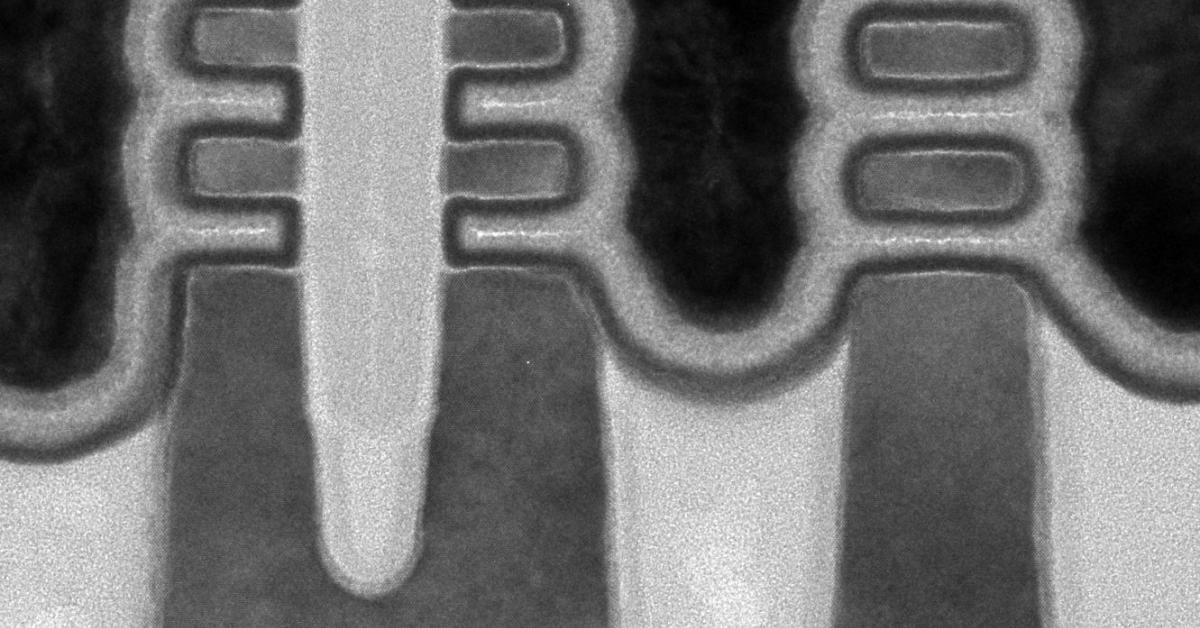

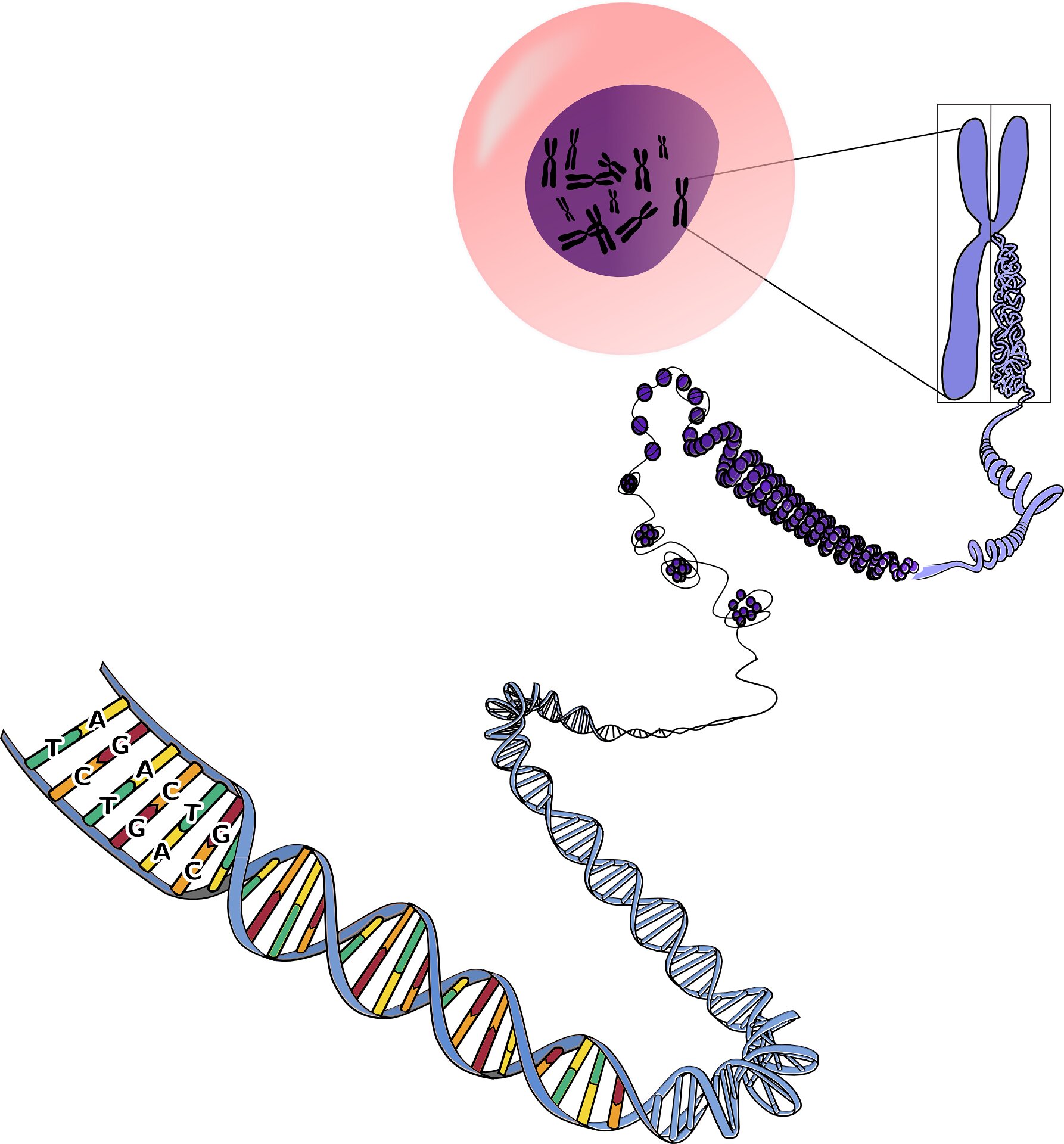

According to the roadmap and on TSMC's 2nm logic section of its website, this next level and brand-new node plans to bring some key technologies to the fold. We're talking about the gate-all-around (GAA) transistor architecture and backside power delivery networks. The payoff of these? Well, they allegedly offer better performance and greater power efficiency than architecture on its N3 node.

The addition of the GAA transistor technology marks a departure from the FinFET designs that have dominated process nodes all the way back since 22nm. While GAA offers better electrostatic control and power efficiency, it's not without its challenges. Manufacturing nanosheet or nanowire structures at scale is like threading a needle blindfolded; it's a highly complex process and as an advanced node, it brings the added pressure of keeping defects to an absolute minimum.