Logic-Compatible Embedded DRAM Architecture for Multifunctional Digital Storage and Compute-in-Memory

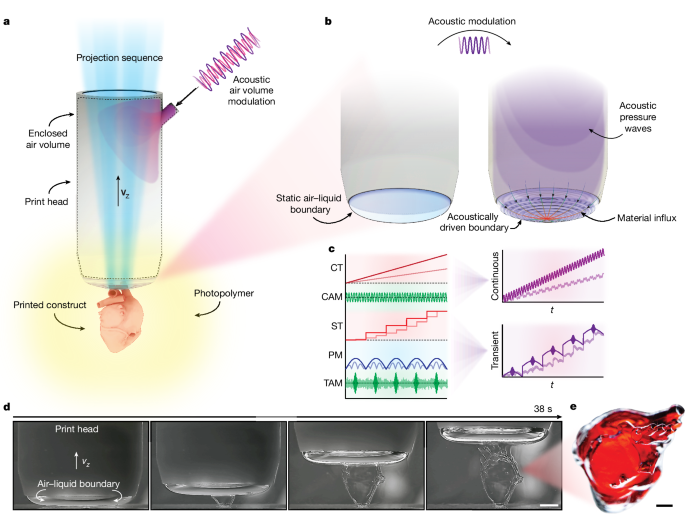

Abstract: The compute-in-memory (CIM) which embeds computation inside memory is an attractive scheme to circumvent von Neumann bottlenecks. This study proposes a logic-compatible embedded DRAM architecture that supports data storage as well as versatile digital computations. The proposed configurable memory unit operates in three modes: (1) memory mode in which it works as a normal dynamic memory, (2) logic–arithmetic mode where it performs bit-wise Boolean logic and full adder operations on two words stored within the memory array, and (3) convolution mode in which it executes digitally XNOR-and-accumulate (XAC) operation for binarized neural networks. A 1.0-V 4096-word × 8-bit computational DRAM implemented in a 45-nanometer CMOS technology performs memory, logic and arithmetic operations at 241, 229, and 224 MHz while consuming the energy of 7.92, 8.09, and 8.19 pJ/cycle. Compared with conventional digital computing, it saves energy and latency of the arithmetic operation by at least 47% and 46%, respectively. For VDD = 1.0 V, the proposed CIM unit performs two 128-input XAC operations at 292 MHz with an energy consumption of 20.8 pJ/cycle, achieving 24.6 TOPS/W. This marks at least 11.9× better energy efficiency and 38.8× better delay, thereby achieving at least 461× better energy-delay product than traditional 8-bit wide computing hardware. Keywords: configurable embedded DRAM; logic operation; arithmetic operation; binary convolution; compute-in-memory

Kim, T.; Chung, Y. Logic-Compatible Embedded DRAM Architecture for Multifunctional Digital Storage and Compute-in-Memory. Appl. Sci. 2024, 14, 9749. https://doi.org/10.3390/app14219749

/cdn.vox-cdn.com/uploads/chorus_asset/file/23954043/VRG_Illo_STK427_Podcasting_playbars.jpg)