TSMC Exploring On-Chip, Semiconductor-Integrated Watercooling

TSMC, at the VLSI symposium, recently presented its investigations into on-chip watercooling as a way to battle issues with heat dissipation. And it involves integrating water channels straight into the chip's design.

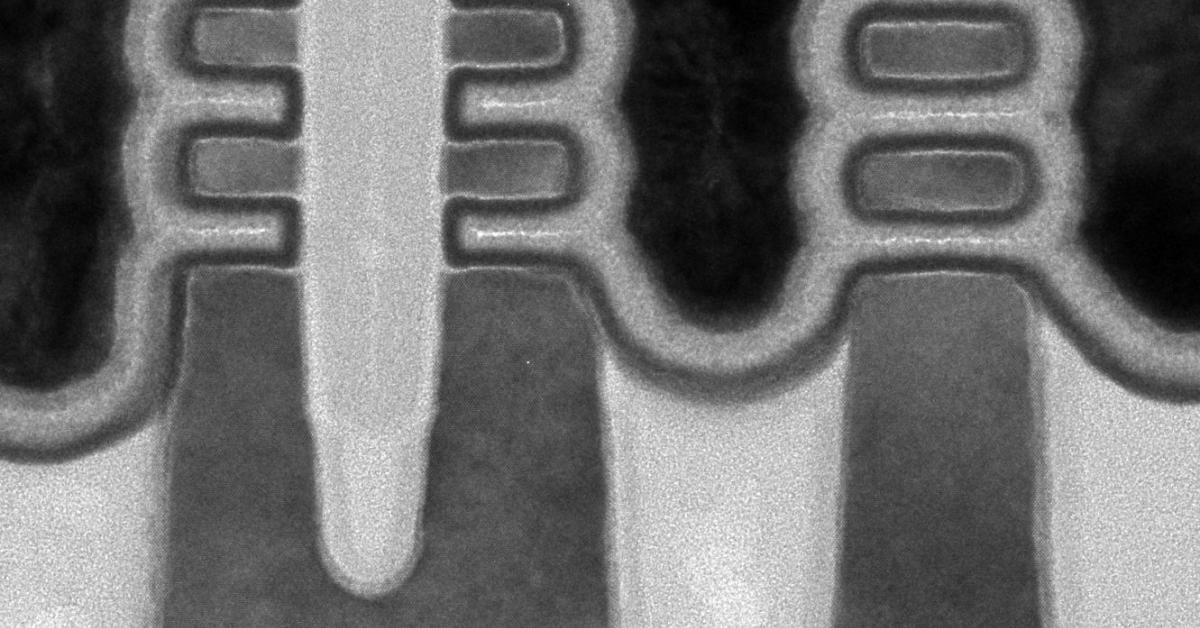

As transistors get increasingly compressed together due to denser manufacturing technologies and added vertical 3D chip stacking, temperature becomes an increasingly critical problem to address. TSMC's researchers think the solution is allowing water to flow in-between sandwiched circuits. It's an incredibly simple theoretical solution, but is an extremely difficult engineering feat to pull off safely --for the electronics, that is.

The mathematics are simple: Current cooling solutions typically work via direct contact with a given chip's heatspreader, direct die contact technologies, or full submersion in a non-conducting fluid. Of these, the first two solutions can only efficiently cool the layers they're directly in contact with, which brings huge problems for vertical chip stacking. The lower layers will have much more trouble dissipating their heat, with of damage or having to throttle, either of which would be bad for performance.

Not only that, but the top layer of the chip will have added strain from having to essentially carry the entire package's heat through to the dissipation layer. And liquid submersion, while efficient and likely better for stacked dies, is expensive and difficult to deploy in professional scenarios that are already geared for air or traditional water cooling.