Research on Multiplication Routine Based on Reconfigurable Four-Valued Logic Processor

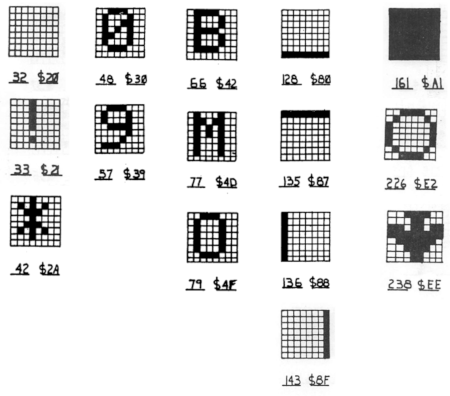

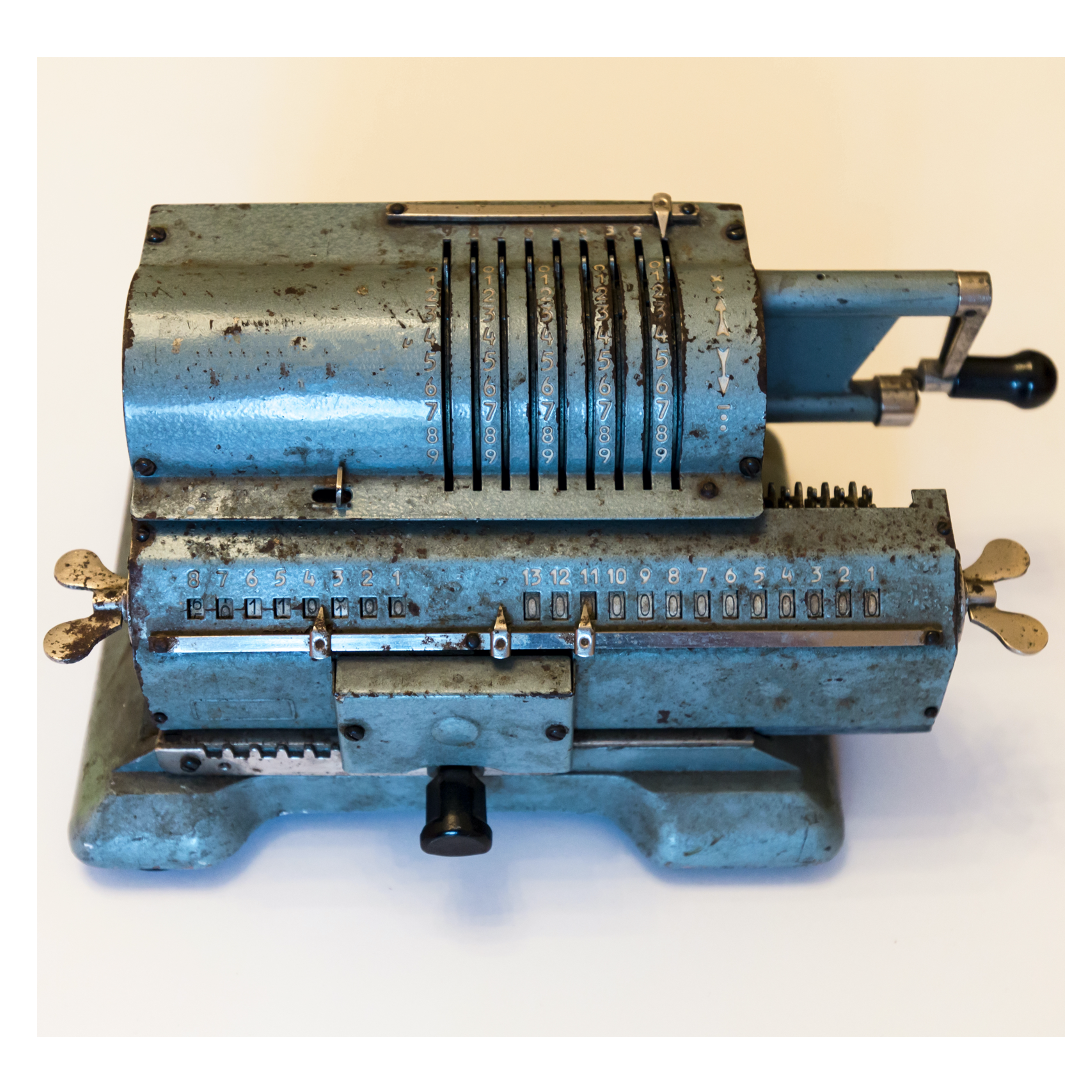

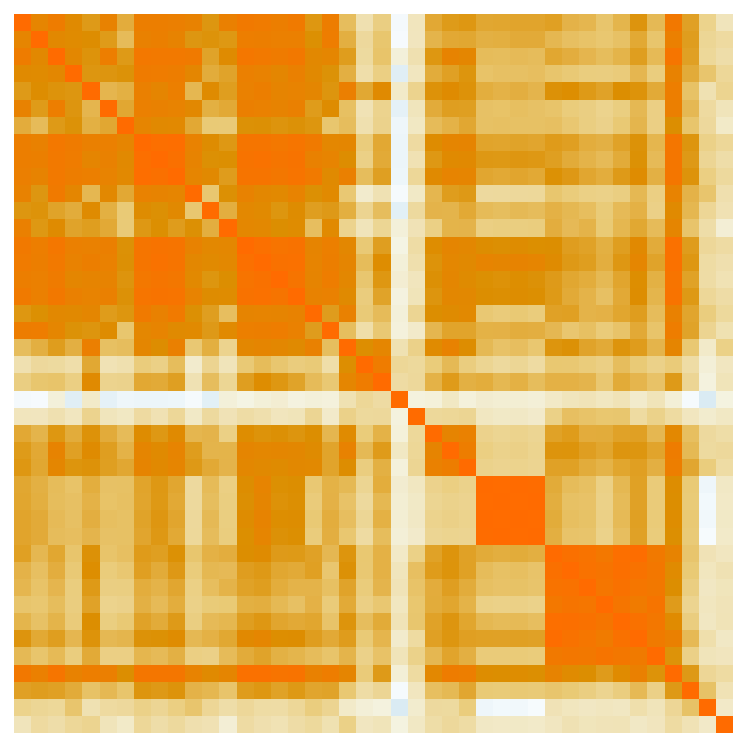

Abstract: Despite the indispensable role of traditional electronic computers in modern society, their limitations in parallel processing capabilities, bit-width constraints, and processor bit-width are becoming increasingly apparent, especially when handling large-scale datasets and complex computational tasks. Although hardware technology and algorithm optimization continue to advance, the arithmetic units of traditional computers—adders—remain constrained by carry delay and bit-width limitations. This bottleneck is particularly pronounced in multiplication operations, mainly when adders are used for partial product accumulation. However, since 2018, the emergence of a new type of Reconfigurable Four-Valued Logic Electronic Processor (RFLEP) has provided a potential solution to these traditional limitations. With its large processor bit-width, flexible bit grouping capabilities, and dynamic hardware function reconfiguration features, this processor has brought revolutionary changes to the field of computing. In this context, this paper proposes and implements a Reconfigurable Four-Valued Logic Multiplication Routine (RFLMR) tailored explicitly for the RFLEP. The RFLMR utilizes the Modified Signed-Digit (MSD) representation method in multi-valued logic combined with the M transformation in four-valued logic to generate partial products. These partial products are then efficiently summed in parallel using the JW-MSD parallel adder, achieving the rapid execution of multiplication operations. Experimental results demonstrate that the multiplication routine based on the RFLEP performs multiplication operations accurately and meets theoretical expectations regarding implementation efficiency and performance. This research not only provides new ideas for developing next-generation high-performance computing systems but also paves the way for exploring more efficient and powerful computing models, heralding a profound transformation in future computing technology. Keywords: reconfigurable four-valued logic electronic processor; reconfigurable four-valued logic multiplication routine; parallel computing; dynamic hardware function reconfiguration; modified signed-digit

Liao, S.; Li, S.; Li, L.; Li, X.; Gu, X.; Zhang, S. Research on Multiplication Routine Based on Reconfigurable Four-Valued Logic Processor. Electronics 2024, 13, 3720. https://doi.org/10.3390/electronics13183720